微電子基石 集成電路設(shè)計探析

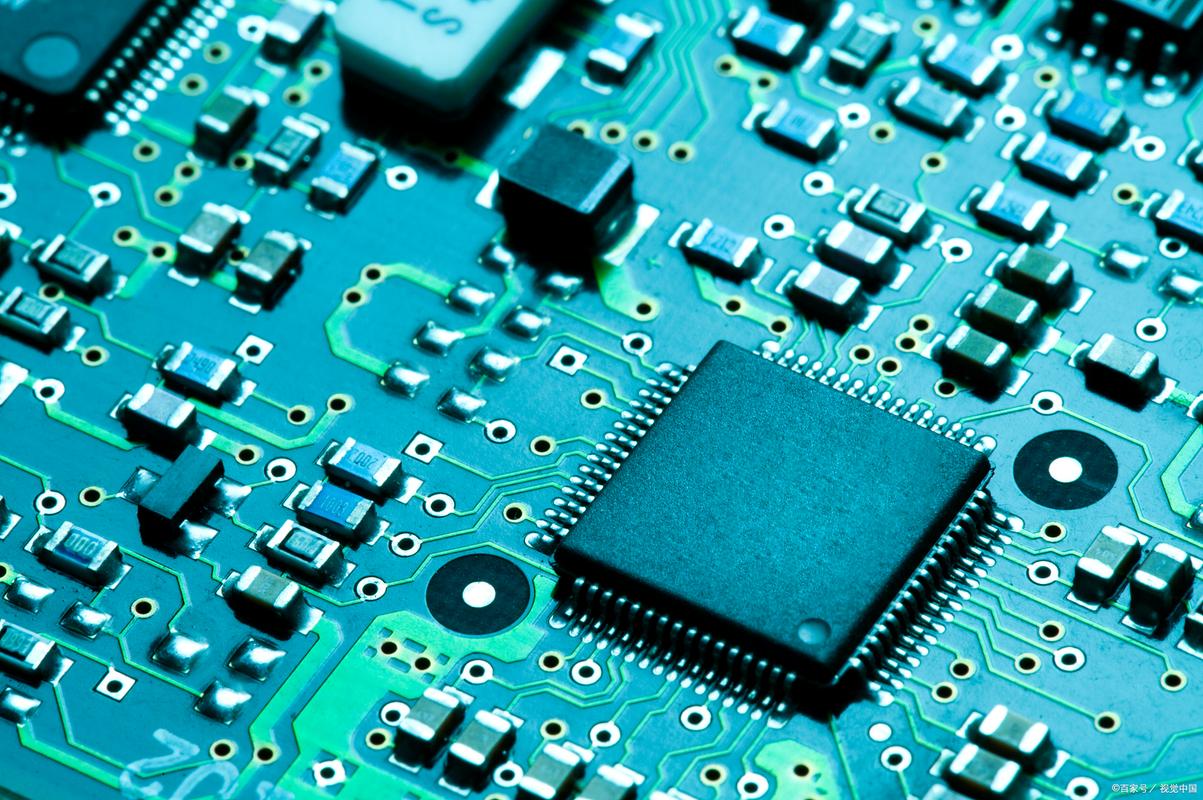

集成電路設(shè)計,作為微電子領(lǐng)域的核心環(huán)節(jié),是現(xiàn)代信息社會的技術(shù)基石。它指的是將數(shù)以億計的晶體管、電阻、電容等電子元件,通過精密的布局與互連,集成在一塊微小的半導(dǎo)體芯片上,以實現(xiàn)特定的電路功能。

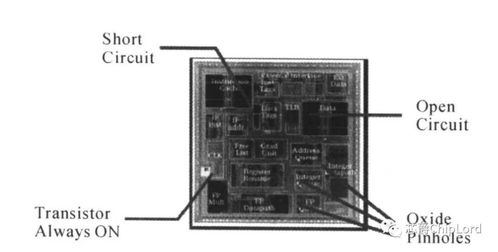

集成電路設(shè)計是一個高度復(fù)雜且多學(xué)科交叉的工程領(lǐng)域,通常可以劃分為前端設(shè)計和后端設(shè)計兩大階段。前端設(shè)計聚焦于邏輯功能的實現(xiàn),包括系統(tǒng)架構(gòu)定義、寄存器傳輸級(RTL)代碼編寫、功能仿真與驗證等環(huán)節(jié)。設(shè)計工程師使用硬件描述語言(如Verilog或VHDL)來“描述”芯片應(yīng)有的行為。后端設(shè)計則負(fù)責(zé)將前端設(shè)計產(chǎn)生的網(wǎng)表轉(zhuǎn)換為可用于制造的物理版圖,涉及布局規(guī)劃、時鐘樹綜合、布線、物理驗證等一系列關(guān)鍵步驟,確保芯片在滿足性能、功耗和面積目標(biāo)的能夠被成功制造。

當(dāng)前,集成電路設(shè)計正面臨著諸多挑戰(zhàn)與機(jī)遇。隨著工藝節(jié)點不斷邁向更小的納米尺度,甚至埃米尺度,物理效應(yīng)日益復(fù)雜,設(shè)計難度呈指數(shù)級增長。功耗、散熱、信號完整性、制造成本等問題變得極為突出。與此新興應(yīng)用如人工智能、5G通信、自動駕駛和物聯(lián)網(wǎng),對芯片的算力、能效和集成度提出了前所未有的高要求,驅(qū)動著設(shè)計方法和工具的不斷創(chuàng)新。

為了應(yīng)對這些挑戰(zhàn),先進(jìn)的設(shè)計理念和技術(shù)不斷涌現(xiàn)。基于IP核的模塊化、可復(fù)用設(shè)計方法極大提升了設(shè)計效率。電子設(shè)計自動化(EDA)工具鏈日益強(qiáng)大,為設(shè)計者提供了從仿真、綜合到驗證的全套解決方案。面向特定領(lǐng)域(DSA)的架構(gòu)、chiplet(小芯片)集成、三維集成電路(3D-IC)等成為重要的發(fā)展方向,旨在突破傳統(tǒng)架構(gòu)的性能和集成瓶頸。

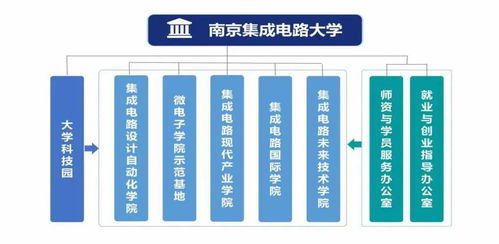

總而言之,集成電路設(shè)計是連接抽象算法與物理實體的橋梁,是驅(qū)動整個半導(dǎo)體產(chǎn)業(yè)前進(jìn)的核心引擎。它的發(fā)展水平直接決定了芯片的性能、功能與創(chuàng)新速度,進(jìn)而深刻影響著從消費電子到國防安全的每一個科技領(lǐng)域。隨著全球?qū)Π雽?dǎo)體自主可控的重視達(dá)到新高度,培養(yǎng)和壯大集成電路設(shè)計人才隊伍,攻克關(guān)鍵核心技術(shù),對于任何一個志在科技前沿的國家而言,都具有不可替代的戰(zhàn)略意義。

如若轉(zhuǎn)載,請注明出處:http://m.hongxin58.cn/product/78.html

更新時間:2026-04-10 21:04:17