2022年超大規模集成電路可測性設計(DFT)技術與實踐 賦能先進芯片設計

隨著半導體工藝持續演進至納米甚至更先進節點,超大規模集成電路(VLSI)的復雜度呈指數級增長,晶體管數量動輒達到數十億乃至數百億。在此背景下,芯片的可測性(Testability)已不再是設計流程的后期附加環節,而是貫穿始終的核心設計約束與關鍵質量指標。2022年,可測性設計(Design for Testability, DFT)技術持續演進,其理論與實踐緊密圍繞提升測試質量、控制測試成本與縮短上市周期三大目標展開,為復雜芯片的成功量產與可靠應用提供了堅實保障。

一、DFT的核心挑戰與技術演進方向

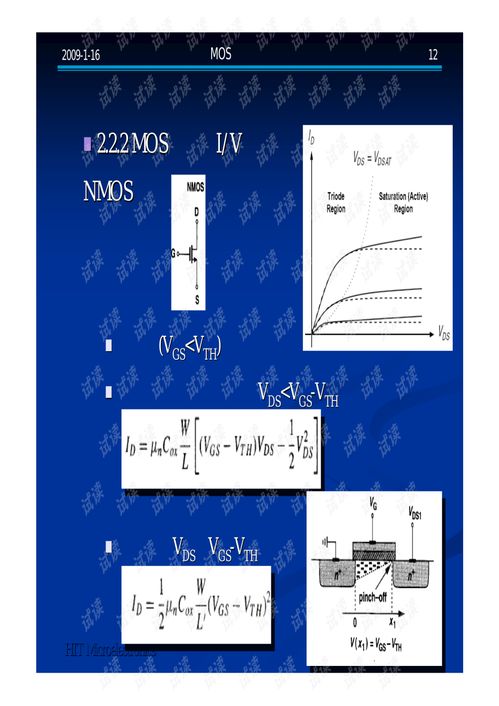

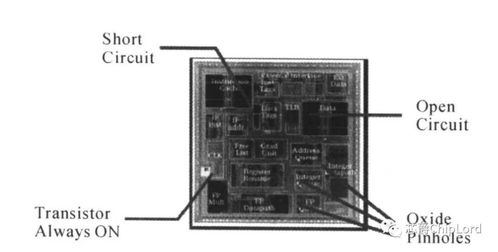

在先進工藝節點,DFT面臨多重挑戰:首先是測試數據量(Test Data Volume)與測試應用時間(Test Application Time)的爆炸式增長,直接推高了測試成本;其次是物理缺陷模型日趨復雜,傳統的固定型故障(Stuck-at Fault)模型已不足以覆蓋全部缺陷,需要引入如轉換時延故障、小延遲缺陷、橋接故障等更精細的模型;低功耗設計、多電壓域、復雜時鐘網絡以及三維集成等技術引入的測試訪問與隔離難題。

針對這些挑戰,2022年的DFT技術與實踐呈現出以下關鍵趨勢:

- 掃描測試(Scan Test)的智能化與壓縮技術深化:自適應掃描壓縮、基于AI的測試模式生成與優化,在保證高故障覆蓋率的顯著壓縮測試向量集。

- 內建自測試(BIST)的廣泛應用與升級:特別是邏輯內建自測試(LBIST)和內存內建自測試(MBIST),不僅用于片上存儲器和邏輯核,更向模擬/混合信號電路、高速接口(如SerDes)和人工智能加速器擴展。

- 面向系統級測試與硅后驗證:DFT架構開始更多考慮芯片在系統板級乃至最終產品中的測試需求,支持系統級測試(SLT)訪問與調試。利用DFT基礎設施進行硅后性能監控、老化監測與現場診斷。

- 與設計流程的早期集成:DFT規劃與實現已大幅提前至架構設計與RTL編碼階段,通過UPF(統一功耗格式)實現多電壓域測試,并利用形式驗證工具確保DFT邏輯的功能正確性。

二、關鍵技術實踐與行業應用

在實踐中,現代DFT流程通常包含以下核心步驟與技術的綜合應用:

- 層次化DFT與測試訪問機制(TAM):對于包含多個IP核的SoC,采用層次化DFT策略,通過標準接口(如IEEE 1500)封裝每個IP的測試邏輯,并利用片上網絡(NoC)或專用TAM高效調度測試數據,實現并行測試,縮短整體測試時間。

- 基于JTAG/IEEE 1149.1/1687(IJTAG)的靈活訪問與控制:JTAG邊界掃描用于板級互聯測試,而更先進的IJTAG網絡則成為訪問和控制片內各類DFT結構(掃描鏈、BIST控制器、傳感器等)的“神經中樞”,極大增強了測試的可控性與可觀測性。

- 功耗感知測試:在測試模式下,大規模電路同時翻轉會引發遠超功能模式的峰值功耗,可能導致電壓下降、熱量積聚甚至芯片損壞。因此,采用測試向量排序、時鐘門控、片上解壓縮器低功耗設計等技術,實施嚴格的測試功耗管理已成為必需。

- 良率學習與診斷驅動良率提升(DDYA):利用DFT產生的失效日志,結合先進診斷軟件,可以精確定位到物理缺陷的位置和類型,反饋至制造廠進行工藝調優,形成“測試-診斷-修復”的閉環,加速良率爬升。

三、未來展望

DFT技術將繼續與人工智能、云計算深度融合。AI將更深度地應用于測試生成優化、故障診斷預測和自適應測試調度。云平臺則為海量測試數據的存儲、分析與協作提供了可能。面對Chiplet(芯粒)和3D IC等異構集成技術,DFT需要發展出跨Die、跨堆疊層的協同測試策略與標準,確保封裝后系統的整體可測試性。

總而言之,在2022年及可預見的DFT已從一項“保險”技術,演變為確保超大規模集成電路設計成功、制造經濟性與產品可靠性的戰略性賦能技術。它要求設計工程師、測試工程師和制造工程師緊密協作,在追求性能、功耗、面積(PPA)極致的將“可測性”基因深刻植入芯片設計的每一個階段。

如若轉載,請注明出處:http://m.hongxin58.cn/product/74.html

更新時間:2026-04-12 11:40:01