Verilog HDL數字集成電路設計原理與應用(第三版) 第7章 仿真測試工具和綜合工具

第7章主要介紹了集成電路設計過程中關鍵的仿真測試工具和綜合工具。在現代數字電路設計中,這些工具是實現高效、準確設計流程的核心組成部分。

一、仿真測試工具的重要性

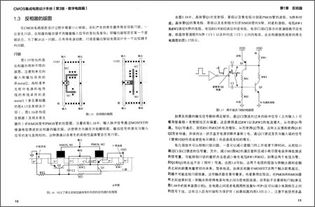

仿真測試是驗證設計功能正確性的關鍵步驟。通過仿真,設計人員可以在實際制造前發(fā)現并修正邏輯錯誤、時序問題等潛在缺陷。常用的仿真工具包括:

- 功能仿真:驗證設計的邏輯功能是否符合規(guī)范,常用工具有ModelSim、VCS等。

- 時序仿真:在考慮電路延遲的情況下驗證設計,確保時序要求得到滿足。

- 測試平臺:使用Verilog編寫測試激勵,模擬各種輸入條件,全面檢驗設計行為。

二、綜合工具的作用與流程

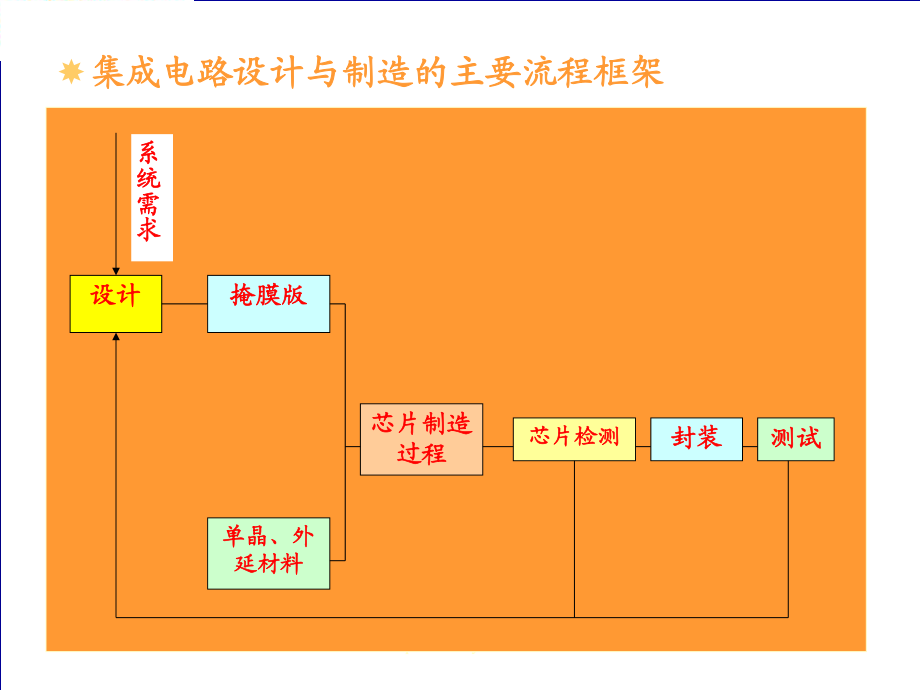

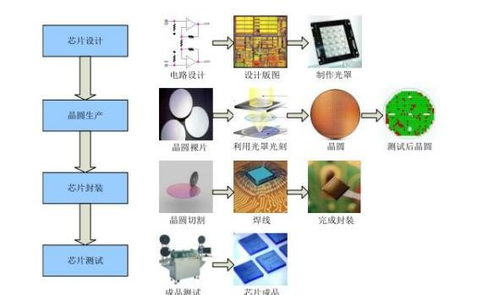

綜合是將高層次設計描述(如Verilog代碼)轉換為門級網表的過程。綜合工具優(yōu)化設計,使其滿足面積、功耗和時序等約束。主要步驟包括:

1. 翻譯:將Verilog代碼轉換為中間表示形式。

2. 優(yōu)化:根據設計約束進行邏輯優(yōu)化,減少資源使用。

3. 映射:將優(yōu)化后的邏輯映射到目標工藝庫的標準單元。

常用工具有Synopsys Design Compiler、Cadence Genus等,它們支持多種優(yōu)化策略,幫助實現高性能、低功耗的設計。

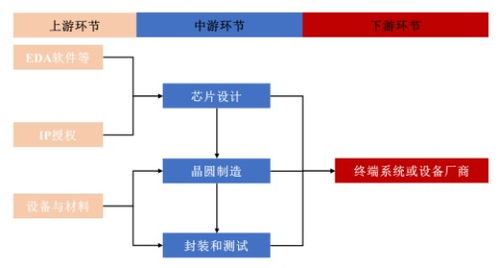

三、工具在集成電路設計中的應用

仿真和綜合工具貫穿于設計流程的各個階段:

- 前端設計:通過仿真驗證功能,再經綜合生成網表。

- 后端設計:結合布局布線工具,進行時序分析和功耗優(yōu)化。

- 驗證:利用仿真結果與預期輸出對比,確保設計可靠性。

四、發(fā)展趨勢與挑戰(zhàn)

隨著工藝節(jié)點的進步,工具需處理更復雜的時序、功耗和信號完整性等問題。未來,人工智能和機器學習技術將被集成到工具中,以提升自動化水平和優(yōu)化效率。

總結,仿真測試工具和綜合工具是數字集成電路設計的支柱。掌握這些工具的使用,對于實現高效、可靠的芯片設計至關重要。設計人員應結合具體項目需求,靈活應用工具,并關注行業(yè)動態(tài),以適應技術發(fā)展。

如若轉載,請注明出處:http://m.hongxin58.cn/product/11.html

更新時間:2026-04-10 15:02:16